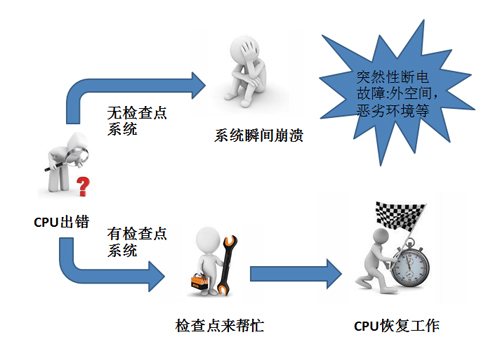

芯片是电子系统的大脑,芯片发生故障会使得整个电子系统瘫痪。当处理器遇到致命故障时通常都通过重启的办法恢复,但这种方法会丢失之前执行状态,可能产生数据被修改、进入错误执行状态、系统瘫痪等严重后果。

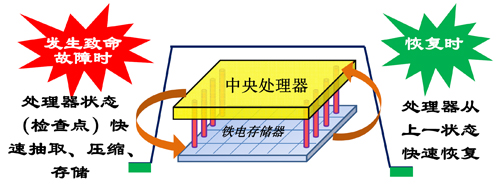

我们利用三维芯片设计思路,将中央处理器和快速非易失的铁电存储器集成到一起,并设计了一个独立硬件,它能周期提取处理器状态,并压缩该状态,快速存储到铁电存储器上。芯片发生致命故障时,处理器系统无法工作,但它断电前的瞬间状态会被保存到非易失性存储器中。恢复后,该处理器能从上一次断电时的场景恢复。由于采用了三维设计和压缩技术,可将恢复间隔缩短至微秒级。这项技术很容易扩展到大型芯片和电子系统中,为一些重要领域的芯片稳定可靠运行提供技术保障。

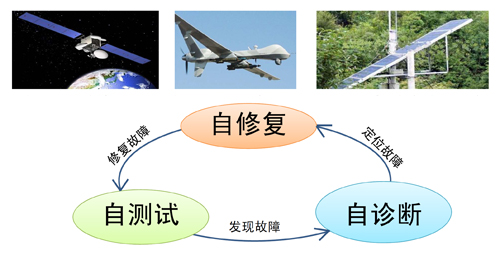

三自(3S)容错设计新原理

在一些空间、尺寸、重量受限制的场景下,传统的多模冗余因开销过大,不再适用,三自(3S)容错设计新原理,能够将容错开销从2-3倍降低到1.x倍。

硬件快速检查点及故障恢复

硬件检查点和故障恢复是实现自修复的一个重要手段,检查点速度可以做到毫秒-秒级,比传统软件检查点方法快3-4个数量级。

本系统展示的就是使用三维芯片思路设计的硬件快速检查点及故障恢复技术。

联系我们

联系我们